Current Status

Not Enrolled

Enroll in this training module to get access

Price

Closed

Get Started

Module Information

About this trainingObjectivesTargeted AudiencePrerequisitesContent SummaryConditionsDurationCertificate

The objective of this module is to be able to use SystemVerilog and UVM to verify an IP using existing UVM Verification Components ( VIP / uVC ), including:

- Be able to use SystemVerilog key language constructs used in verification

- Be able to instantiate Verification IPs and create a UVM testbench.

- Be able to implement coverage metrics in line with a verification plan to report verification progress

- Be able to implement checkers using scoreboards and simple assertions

Digital Microelectronics Engineers starting with SystemVerilog and UVM

Students registered to this course should have a minimum of digital design engineering background:

- General hardware design and architecture knowledge

- Basic scripting know-how

- Basic programming know-how (C , Python , … )

- Knowledge of a Hardware Description Language such as VHDL or Verilog

- Simulation know-howwith a waveform viewer and coverage features

- English B2

In this course, students will learn how the fundamentals of SystemVerilog and UVM:

- SystemVerilog Language Fundamentals

- SystemVerilog for Coverage Driven Verification

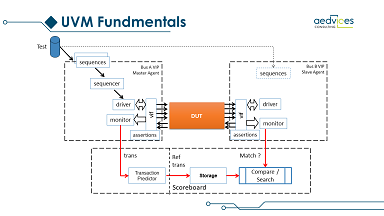

- UVM Fundamentals

- UVM Must Know

- Course openned within 1 to 3 months prior to start

- Subject to validation of the prerequisites and objectives survey

- Learners should have legal and valid accesses to one of the following simulators from their employers:

- SIEMENS Questa

- CADENCE Xcelium

- SYNOPSYS VCS

- English Level B2 minimum

| Online Content Time | 14h |

| Est. Indep. Learning Time | 14h |

| Workshop time | 7h |

| Live Integratin Time | 4.5h |

| Est. Prep. Time | 45min |

| Checkpoint Time | 30min |

A certificate of success will be delivered after completion of 60% of the labs and a score of 60% on the final checkpoint

PDF Files are available in each individual presentation following the Download tab.

Average Review Score:

★★★★★

You must log in and have started this training module to submit a review.

Training Module Content

section: General Info

2 Course Components

You don't currently have access to this content

section: SystemVerilog Fundamentals

10 Course Components

|

3 Checks

You don't currently have access to this content

Section Content

0% Complete

0/10 Steps

section: SystemVerilog for Coverage Driven Verification

9 Course Components

|

6 Checks

You don't currently have access to this content

Section Content

0% Complete

0/9 Steps

section: UVM Environment & Testbench

14 Course Components

|

4 Checks

You don't currently have access to this content

Section Content

0% Complete

0/14 Steps

UVMU_LI03_SLD: Live Integration (preparation ~5 minutes / meeting 90 minutes)

Live Meeting (Required)

section: UVM Must Know

2 Course Components

You don't currently have access to this content

Section Content

0% Complete

0/2 Steps

section: UVMU Workshop

1 Course Component

You don't currently have access to this content

Section Content

0% Complete

0/1 Steps

UVMU_WS01_SLD: UVMU Workshop ( meetings 2x 3.5 hours )

Live Meeting (Required)

section: UVMU checkpoint

5 Course Components

You don't currently have access to this content

CPT_CHK: Live Checkpoint

You don't currently have access to this content