TM101 – SystemVerilog Fundamentals for Verification

This module goes through the main SystemVerilog elements used in verification:

-

- General Syntax

- Notion of interfaces

- Object Oriented Programming

- Constrained Random Generation

- Functional Coverage

TM102 – SystemVerilog for RTL Design

This module goes trough the main SystemVerilog design constructs.

- Review of the main Verilog syntax (module, reg, always, assign, …)

- SystemVerilog types (logic, struct, arrays, …)

- Interfaces

- Packages

- Testbenches using SystemVerilog classes, random generation

TM103: SVA for Designers

-

- Introduction to Assertions

- Design Assertions vs Functional Assertions

- The different types of SystemVerilog Assertions

- The main SystemVerilog assertions operators

- Simulation vs Formal

- Using a formal tool to verify simple assertions

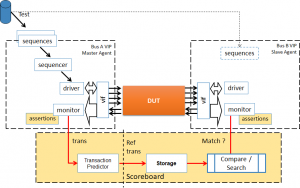

TM202 – UVM Know-How for Verification Engineers

-

- UVM main classes

- Phases

- The configuration db

- Objections

- Agent structure (agent, driver, monitor, sequencer, virtual interface, configuration)

- Scoreboards

TM250 – Advanced Verification using SystemVerilog and UVM

-

- UVM Callback & Factory

- Advanced Sequences

- Register Abstraction Layer Modeling

- Build a Verification IP

- DPI-C

- TLM ports

VS201-CMN – Verification Fundamentals

Common courses for all Verification School (VS) modules:

- Introduction to Verification

- Debug Methodology to gain in productivity

- Verifier’s guide to On-Chip Buses, Interconnects and External I/Os

- Makefile and Scripting with TCL

VS202-VPM – Verification Project Management

-

- Verification as a process

- The different types of verification strateges and approaches

- Verification Project Reporting using Metrics and Coverage

- Build a Verification Plan

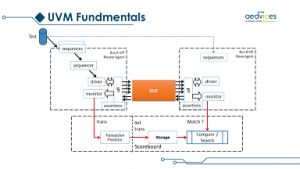

VS203-UVMU – Verification Methodology using UVM

- SystemVerilog Fundamentals

- SystemVerilog for Coverage Driven Verification

- UVM Fundamentals

- UVM Must Know